AMD Epyc Genoa z 12 przedstawionymi chipletami

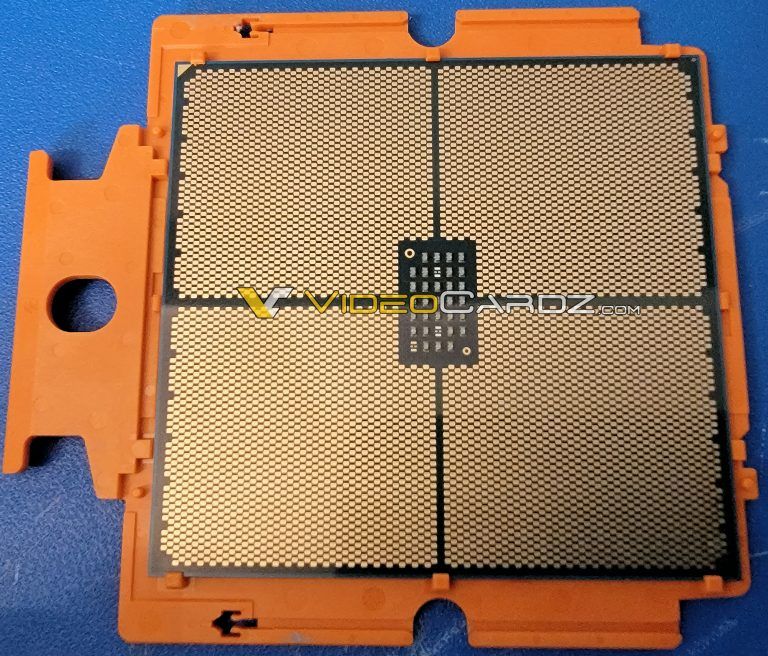

tylko wczoraj Pojawił się pierwszy obraz nowego gniazda SP5 (LGA6096) i teraz możemy wreszcie zobaczyć procesor nowej generacji EPYC bez wbudowanego rozpraszacza ciepła.

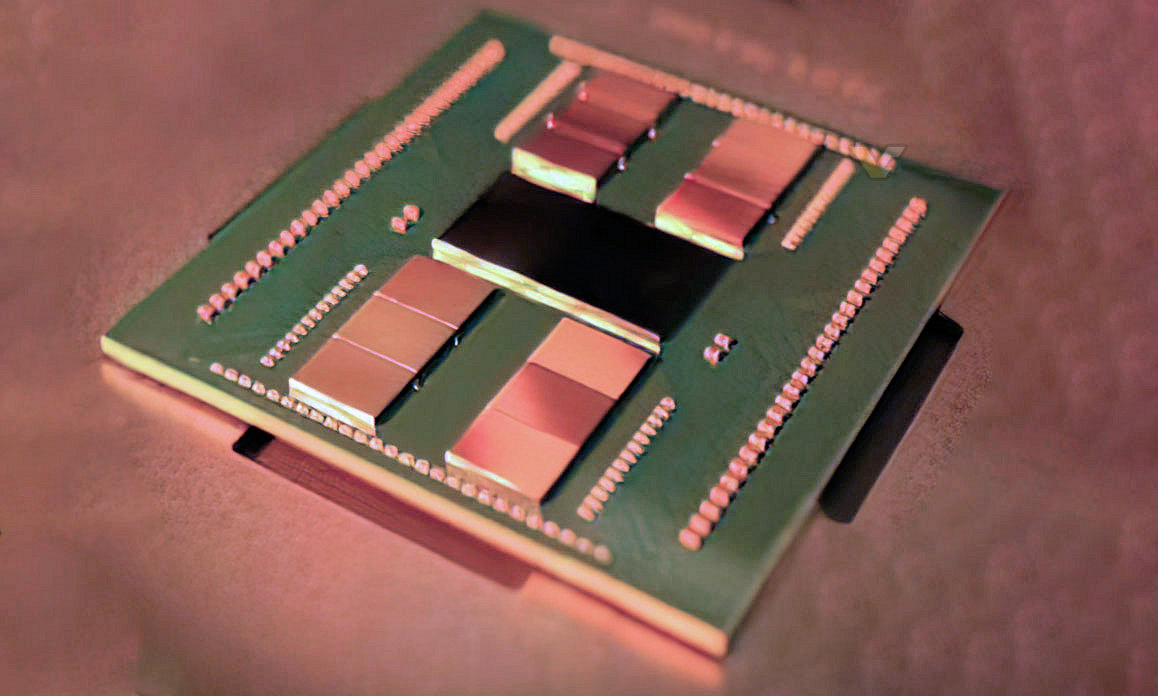

Członek forum Chiphell „zhangzhonghao” wydaje się być pierwszą osobą, która ujawniła prawdziwy obraz nadchodzącego procesora serwerowego Zen4, o nazwie kodowej Genoa. To jest pierwszy obraz, który pokazuje wszystkie 12 chipletów zainstalowanych w SP5.

Procesor AMD EPYC „Genua”, źródło: Chiphell

EPYC Genoa zawiera do 96 rdzeni i 192 serie w swoim pełnym składzie. AMD wyda kilka SKU z częściowo uszkodzonymi rdzeniami, więc tylko dlatego, że ten procesor ma 12 chipów, nie oznacza to, że będzie miał wszystkie 96 rdzeni.

Każda matryca Zen4 CCD ma powierzchnię 72 mm², czyli o 8 mm² mniejszą niż Zen3 (np. seria EPYC „Milan”). Matryca I/O jest również mniejsza, ma około 397 mm² w porównaniu do 416 mm² w procesorach Zen3 EPYC. Jednak AMD nie miało problemu z zainstalowaniem 6 chipów po każdej stronie matrycy I/O, biorąc pod uwagę, że pakiet SP5 (LGA 6096) jest o 37% większy niż SP3.

AMD 16-rdzeniowy procesor EPYC Genoa, źródło: VideoCardz

Nowa platforma AMD SP5 będzie obsługiwać do 12 kanałów pamięci DDR5 oprócz interfejsu PCIe Gen5. AMD Genoa już jest dostarczana do wczesnych klientów, według AMD. Nowa seria EPYC 7004 jest obecnie w drodze do wprowadzenia na rynek pod koniec tego roku.

| Specyfikacje rzekomych procesorów z serii AMD EPYC | ||||||

|---|---|---|---|---|---|---|

| Karty graficzne | 7001 „Neapol” | 7002 „Rzym” | 7003 „Mediolan” 7003 „Mediolan-X” |

7004 „Genua” | 7004 „Bergamo” | |

| 7005 „Tauryna” | początek | 2017 | 2019 | 2021 | 2022 | 2022 |

| 2023/2024 | budynek | 14 nm cynk | 7 nm Zen 2 | 7 nm Zen 3 | 5 nm Zen4 | 5 nm Zen4c |

| Zain 5 | Wtyczka | SP3 (LGA4094) | SP3 (LGA4094) | SP3 (LGA4094) | SP5 (LGA-6096) | SP5 (LGA-6096) |

| SP5 (LGA-6096) | Moduły/plastry | 4xCCD | 8xCCD + 1xIOD | 8xCCD + 1xIOD | 12xCCD + 1xIOD | 12xCCD + 1xIOD |

| TBC | ||||||

| Maksymalna liczba rdzeni | Maksymalny zegar | TBC | TBC | |||

| TBC | Pamięć podręczna L2 na centrum | 0,5 MB | 0,5 MB | 0,5 MB | 1 megabajt | TBC |

| TBC | Pamięć podręczna L3 na CCX | 8 MB | 8 MB | 32MB / 96MB | 32 MB | |

| TBC | ||||||

| TBC | ||||||

| kanały pamięci | Obsługa pamięci | linie PCIe | ||||

| TBC | TBC | |||||

Maks. cTDP TBC źródło: zhangzhonghao @pawel

Przez @9550pro

„Specjalista sieciowy. Odwieczny maniak zombie. Kawowy ninja. Przyjazny dla hipsterów analityk.”